デマルチプレクサは、1 つの入力ラインと 2 つの入力ラインのみを備えた組み合わせ回路です。N出力行。簡単に言えば、マルチプレクサは単一入力と複数出力の組み合わせ回路です。情報は単一の入力ラインから受信され、出力ラインに送られます。選択ラインの値に基づいて、入力はこれらの出力の 1 つに接続されます。デマルチプレクサはマルチプレクサの反対側にあります。

エンコーダやデコーダとは異なり、選択ラインは n 行と 2 行あります。n出力。つまり、合計2つありますn入力の可能な組み合わせ。デマルチプレクサも次のように扱われます。 デマルチプレクサ 。

デマルチプレクサには次のようなさまざまなタイプがあります。

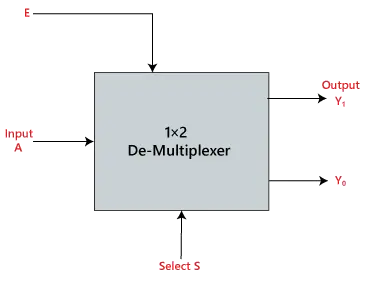

1×2 デマルチプレクサ:

1 to 2 デマルチプレクサには、出力が 2 つだけあります。つまり、Y0、Y1、1 つの選択ライン、つまり S0、および単一入力、つまり A。選択値に基づいて、入力は出力の 1 つに接続されます。 1のブロック図と真理値表 × 2 つのマルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

そして0=S0'.A

そして1=S0.A

上記の式の論理回路は次のとおりです。

モニターのサイズを決める方法

1×4 デマルチプレクサ:

1 ~ 4 デマルチプレクサでは、合計 4 つの出力、つまり Y があります。0、 そして1、 そして2、Y3、2 つの選択ライン、つまり S0そしてS1選択ライン S に存在する入力の組み合わせに基づいて、単一の入力、つまり A0そしてS1、入力は出力の 1 つに接続されます。 1のブロック図と真理値表 × 4つのマルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

そして0=S1'S0「あ」

そして1=S1'S0あ

そして2=S1S0「あ」

そして3=S1S0あ

上記の式の論理回路は次のとおりです。

1×8 デマルチプレクサ

1 ~ 8 デマルチプレクサには、合計 8 つの出力があります。つまり、Y0、 そして1、 そして2、 そして3、 そして4、 そして5、 そして6、Y7、3 つの選択ライン、つまり S0、S1そしてS2選択ライン S に存在する入力の組み合わせに基づいて、単一の入力、つまり A0、S1そしてS2、入力はこれらの出力のいずれかに接続されます。 1のブロック図と真理値表 × 8 つのデマルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

そして0=S0'.S1'.S2'.A

そして1=S0.S1'.S2'.A

そして2=S0'.S1.S2'.A

そして3=S0.S1.S2'.A

そして4=S0'.S1'.S2あ

そして5=S0.S1'.S2あ

そして6=S0'.S1.S2あ

そして7=S0.S1.S3.A

上記の式の論理回路は次のとおりです。

1×4および1×2デマルチプレクサを使用した1×8デマルチプレクサ

1を実装できます × 低次デマルチプレクサを使用する 8 デマルチプレクサ。 1を実装するには × 8 デマルチプレクサ、2 つ必要です 1 × 4 つのデマルチプレクサと 1 つの 1 × 2デマルチプレクサ。 1 × 4 マルチプレクサには 2 つの選択ライン、4 つの出力、1 つの入力があります。 1 × 2 デマルチプレクサには選択ラインが 1 つだけあります。

8 つのデータ出力を取得するには、1 が 2 つ必要です。 × 4デマルチプレクサ。 1×2 デマルチプレクサは 2 つの出力を生成します。したがって、最終出力を取得するには、1×2 デマルチプレクサの出力を両方の 1×2 デマルチプレクサの入力として渡す必要があります。 × 4デマルチプレクサ。 1のブロック図 × 1 を使用する 8 デマルチプレクサー × 4と1 × 2 デマルチプレクサを以下に示します。

C++でintを文字列に変換する

1×16デマルチプレクサ

1×16 デマルチプレクサでは、合計 16 個の出力、つまり Y があります。0、 そして1、 …、 そして16、4 つの選択ライン、つまり S0、S1、S2、S3選択ライン S に存在する入力の組み合わせに基づいて、単一の入力、つまり A0、S1、S2、入力はこれらの出力のいずれかに接続されます。 1のブロック図と真理値表 × 16 個のデマルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

そして0=A.S0'.S1'.S2'.S3'

そして1=A.S0'.S1'.S2'.S3

そして2=A.S0'.S1'.S2.S3'

そして3=A.S0'.S1'.S2.S3

そして4=A.S0'.S1.S2'.S3'

そして5=A.S0'.S1.S2'.S3

そして6=A.S0'.S1.S2.S3'

そして7=A.S0'.S1.S2.S3

そして8=A.S0.S1'.S2'.S3'

そして9=A.S0.S1'.S2'.S3

そして10=A.S0.S1'.S2.S3'

そして十一=A.S0.S1'.S2.S3

そして12=A.S0.S1.S2'.S3'

そして13=A.S0.S1.S2'.S3

そして14=A.S0.S1.S2.S3'

そして15=A.S0.S1.S2'.S3

上記の式の論理回路は次のとおりです。

1×8 および 1×2 デマルチプレクサを使用した 1×16 デマルチプレクサ

1を実装できます × 低次デマルチプレクサを使用する 16 デマルチプレクサ。 1を実装するには × 16 デマルチプレクサ、2 つ必要です 1 × 8 つのデマルチプレクサと 1 つの 1 × 2デマルチプレクサ。 1 × 8 マルチプレクサには 3 つの選択ライン、1 つの入力、8 つの出力があります。 1 × 2 デマルチプレクサには選択ラインが 1 つだけあります。

16 個のデータ出力を取得するには、2 つの 1×8 デマルチプレクサーが必要です。 1 × 8 デマルチプレクサは 8 つの出力を生成します。したがって、最終出力を取得するには、1 が必要です。 × 2 デマルチプレクサーにより、1 つの入力から 2 つの出力が生成されます。次に、これらの出力を両方のデマルチプレクサーに入力として渡します。 1のブロック図 × 16 デマルチプレクサ 1 を使用 × 8と1 × 2 デマルチプレクサを以下に示します。