マルチプレクサは 2 つの組み合わせ回路です。n入力ラインと 1 つの出力ライン。簡単に言えば、マルチプレクサは複数の入力と単一の出力を組み合わせた回路です。バイナリ情報は入力ラインから受信され、出力ラインに送られます。選択ラインの値に基づいて、これらのデータ入力の 1 つが出力に接続されます。

整数から文字列へ

エンコーダやデコーダとは異なり、選択ラインは n つ、選択ラインは 2 つあります。n入力行。つまり、合計2つありますN入力の可能な組み合わせ。マルチプレクサも次のように扱われます。 マックス 。

マルチプレクサには次のようなさまざまなタイプがあります。

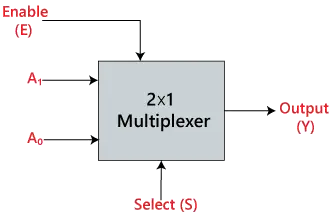

2×1マルチプレクサ:

2×1 マルチプレクサでは、入力は 2 つだけです。つまり、A0そしてA1、1 つの選択ライン、つまり S0選択ライン S に存在する入力の組み合わせに基づいて、単一の出力、つまり Y。0、これら 2 つの入力のうちの 1 つが出力に接続されます。 2のブロック図と真理値表 × 1 マルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

Y=S0'.A0+S0.A1

上式の論理回路は以下の通りです。

4×1マルチプレクサ:

4×1 マルチプレクサには、合計 4 つの入力があります。つまり、A0、A1、A2、A3、2 つの選択ライン、つまり S0そしてS1選択ライン S に存在する入力の組み合わせに基づいて、単一の出力、つまり Y0そしてS1、これら 4 つの入力のうちの 1 つが出力に接続されます。 4つのブロック図と真理値表 × 1 マルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

Y=S1'S0「あ」0+S1'S0あ1+S1S0「あ」2+S1S0あ3

上式の論理回路は以下の通りです。

8対1マルチプレクサ

8 対 1 マルチプレクサには、合計 8 つの入力があります。つまり、A0、A1、A2、A3、A4、A5、A6、A7、3 つの選択ライン、つまり S0、S1そしてS2選択ライン S に存在する入力の組み合わせに基づいて、単一の出力、つまり Y0、S1、そしてS2、これら 8 つの入力のうちの 1 つが出力に接続されます。 8のブロック図と真理値表 × 1 マルチプレクサを以下に示します。

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

Y=S0'.S1'.S2'.A0+S0.S1'.S2'.A1+S0'.S1.S2'.A2+S0.S1.S2'.A3+S0'.S1'.S2あ4+S0.S1'.S2あ5+S0'.S1.S2.A6+S0.S1.S3.A7

上式の論理回路は以下の通りです。

4×1および2×1マルチプレクサを使用した8×1マルチプレクサ

8つを実装できます × 1 マルチプレクサは下位マルチプレクサを使用します。 8を実装するには × マルチプレクサは 1 つですが、2 つ必要です 4 × 1 つのマルチプレクサと 1 つの 2 × 1マルチプレクサ。 4 × 1 つのマルチプレクサには 2 つの選択ライン、4 つの入力、および 1 つの出力があります。 2 × 1 つのマルチプレクサには選択ラインが 1 つだけあります。

8 つのデータ入力を取得するには、2 つの 4 が必要です。 × 1マルチプレクサ。 4 × 1 つのマルチプレクサは 1 つの出力を生成します。したがって、最終出力を取得するには、2 が必要です。 × 1マルチプレクサ。 8のブロック図 × 4 を使用する 1 マルチプレクサ × 1と2 × 1 マルチプレクサを以下に示します。

16対1マルチプレクサ

16 対 1 マルチプレクサには、合計 16 個の入力があります。0、A1、…、A16、4 つの選択ライン、つまり S0、S1、S2、S3選択ライン S に存在する入力の組み合わせに基づいて、単一の出力、つまり Y0、S1、S2、これら 16 個の入力の 1 つが出力に接続されます。 16のブロック図と真理値表 × 1

ブロック図:

真理値表:

項 Y の論理式は次のとおりです。

Y=A0.S0'.S1'.S2'.S3'+A1.S0'.S1'.S2'.S3+A2.S0'.S1'.S2.S3'+A3.S0'.S1'.S2.S3+A4.S0'.S1.S2'.S3'+A5.S0'.S1.S2'.S3+A6.S1.S2.S3'+A7.S0'.S1.S2.S3+A8.S0.S1'.S2'.S3'+A9.S0.S1'.S2'.S3+Y10.S0.S1'.S2.S3'+A11.S0.S1'.S2.S3+A12S0.S1.S2'.S3'+A13.S0.S1.S2'.S3+A14.S0.S1.S2.S3'+A15.S0.S1.S2'.S3上式の論理回路は以下の通りです。

8×1および2×1マルチプレクサを使用した16×1マルチプレクサ

16 を実装できます。 × 1 マルチプレクサは下位マルチプレクサを使用します。 8を実装するには × マルチプレクサは 1 つですが、8 が 2 つ必要です × マルチプレクサ 1 個と 2 マルチプレクサ 1 個 × 1マルチプレクサ。 8 × 1 つのマルチプレクサには 3 つの選択ライン、4 つの入力、および 1 つの出力があります。 2 × 1 つのマルチプレクサには選択ラインが 1 つだけあります。

16 個のデータ入力を取得するには、2 つの 8 × 1 マルチプレクサーが必要です。 8 × 1 つのマルチプレクサは 1 つの出力を生成します。したがって、最終出力を取得するには、2 が必要です。 × 1マルチプレクサ。 16のブロック図 × 8を使用する1つのマルチプレクサ × 1と2 × 1 マルチプレクサを以下に示します。